【導(dǎo)讀】直接數(shù)據(jù)頻率合成器(DDS)因能產(chǎn)生頻率捷變且殘留相位噪聲性能卓越而著稱。另外,多數(shù)用戶都很清楚DDS輸出頻譜中存在的雜散噪聲,比如相位截?cái)嚯s散以及與相位-幅度轉(zhuǎn)換過程相關(guān)的雜散等。此類雜散是實(shí)際DDS設(shè)計(jì)中的 有限相位和幅度分辨率造成的結(jié)果。

直接數(shù)據(jù)頻率合成器(DDS)因能產(chǎn)生頻率捷變且殘留相位噪聲性能卓越而著稱。另外,多數(shù)用戶都很清楚DDS輸出頻譜中存在的雜散噪聲,比如相位截?cái)嚯s散以及與相位-幅度轉(zhuǎn)換過程相關(guān)的雜散等。此類雜散是實(shí)際DDS設(shè)計(jì)中的 有限相位和幅度分辨率造成的結(jié)果。

其他雜散源與集成DAC相關(guān)——DAC的采樣輸出產(chǎn)生基波和相關(guān)諧波的鏡像頻率。另外,因DAC非理想的開關(guān)屬性可能導(dǎo)致低階諧波的功率水平升高。最后一種雜散源是在系統(tǒng)時(shí)鐘頻率的基波與任何內(nèi)部分諧波時(shí)鐘之間產(chǎn)生的混頻產(chǎn)物。

上述雜散噪聲的全部已知來源都可根據(jù)相對(duì)于DDS/DAC輸出處基波信號(hào)的頻率偏移進(jìn)行預(yù)測(cè)。以下內(nèi)容旨在幫助您確定DDS輸出信號(hào)頻譜中的雜散源。如果通過改變DDS頻率調(diào)諧字使雜散與DDS/DAC相關(guān),則并不難確定雜散源。這是因?yàn)楦淖冋{(diào)諧字時(shí),上述所有雜散噪聲的頻率偏移均隨基波變化。

如何確定DDS輸出信號(hào)頻譜中的雜散源

例如,24 MHz基波有一個(gè)72 MHz的三階諧波。如果DDS系統(tǒng)時(shí)鐘為100 MHz,則三階諧波與系統(tǒng)時(shí)鐘的產(chǎn)物會(huì)折回到至28 MHz,與基波僅偏移4 MHz。如果基波增加10 KHz至24.010 MHz,則新的后疊積將偏移基波3.97MHz,這是可以提前預(yù)測(cè)的。

如果無論頻率調(diào)諧字如何變化,雜散相對(duì)基波的頻率偏移均保持不變,則DDS/DAC不是雜散源。相反,如果雜散相對(duì)基波的頻率偏移隨DDS調(diào)諧改變而變化,則DDS/DAC很可能是雜散源。通過確保頻率調(diào)諧字變化包括頻率調(diào)諧字的截?cái)嗖糠趾臀唇財(cái)嗖糠郑蔀榘l(fā)現(xiàn)雜散源帶來方便。截?cái)嗖糠忠话銥檎{(diào)諧字的14位至19位(MSB)。

當(dāng)DDS頻率調(diào)諧字發(fā)生變化時(shí),相對(duì)基波(載波)的頻率偏移不發(fā)生改變的雜散一般分為兩類:

要么以某種方式耦合至DDS電源;

要么是驅(qū)動(dòng)DDS的參考時(shí)鐘源上的一個(gè)元件。

注意,如果DDS的內(nèi)部參考時(shí)鐘乘法器(PLL)被啟用,則DDS輸出同樣存在相對(duì)于基波的固定邊帶雜散,其頻率偏移等于參考時(shí)鐘頻率。

參考時(shí)鐘源雜散

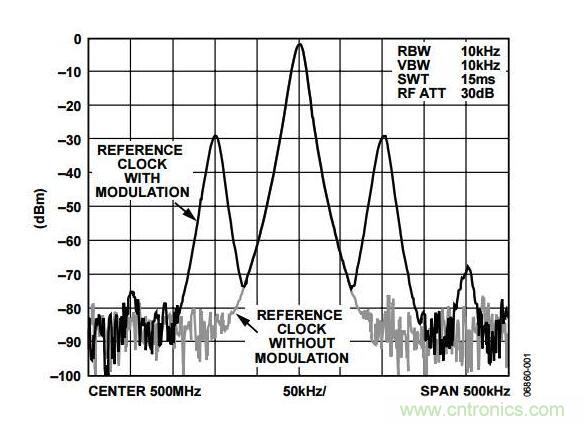

圖1所示為DDS的500 MHz參考時(shí)鐘,由一個(gè)100 KHz音實(shí)現(xiàn)10%的AM調(diào)制。該參考時(shí)鐘源是一款Rohde andSchwartz具有調(diào)制功能的SMA信號(hào)發(fā)生器。圖1中的灰色線為無調(diào)制條件下的參考時(shí)鐘。

圖1. DDS的500 MHz參考時(shí)鐘

(由一個(gè)100 kHz音(藍(lán)色線)實(shí)現(xiàn)10%的AM調(diào)制)

圖2中,同一100 KHz音以完全相同的頻率偏移傳輸?shù)紻DS/DAC輸出,不受調(diào)諧字頻率影響。圖2中的頻率調(diào)諧字表現(xiàn)出四個(gè)相互疊加的不同DDS載波。注意,在全部四個(gè)載波改變時(shí),參考時(shí)鐘雜散的頻率偏移保持不變;但該雜散的幅度以20 log(x)為單位發(fā)生變化,其中,x為參考時(shí)鐘頻率與DDS載波頻率之比。

圖2. 四個(gè)DDS輸出載波表現(xiàn)出100 kHz雜散產(chǎn)生的效應(yīng),該雜散對(duì)DDS的參考時(shí)鐘(500 MHz)進(jìn)行AM調(diào)制

開關(guān)電源雜散

圖3和圖4展示了DDS電源上的雜散(如開關(guān)電源)與DDS輸出之間的關(guān)系。注意,如前所述,在相對(duì)于相同的載波變化時(shí),它們也保持相同的固定頻率偏移。

圖3. 四個(gè)DDS輸出載波表現(xiàn)出150 kHz雜散產(chǎn)生的效應(yīng),該雜散對(duì)DDS的電源進(jìn)行AM調(diào)制

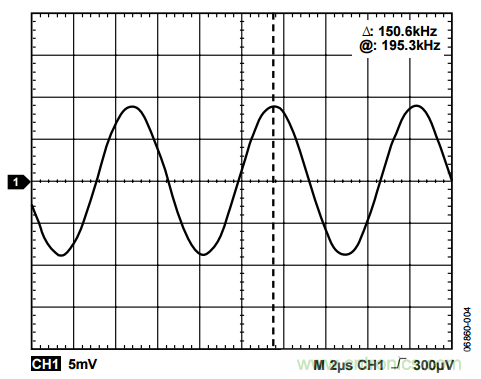

圖4為DDS電源的實(shí)際時(shí)域,其中,一個(gè)150 kHz調(diào)制音施加于DDS電源之上,以仿真電源開關(guān)雜散。

圖4. 150 kHz音(16 mV p-p)通過一個(gè)函數(shù)發(fā)生器施加于DDS電源之

DDS參考時(shí)鐘或電源(一般為AVDD)上的雜散會(huì)對(duì)DDS輸出產(chǎn)生一定的影響。結(jié)果,當(dāng)載波變化時(shí),以載波為中心的邊帶將保持不變。因此,調(diào)諧字發(fā)生變化時(shí),如果在DAC/DDS輸出中觀察到固定雜散,則應(yīng)檢查參考時(shí)鐘源和DDS電源中是否存在雜散。