【導讀】一直以來,設計人員都將最小化功耗的工作留給實現/物理工具來完成。但到了這個時候,有關設計的所有重要架構和微架構決策都已確定。物理工具對功耗的影響非常有限。這些工具無法對設計架構進行徹底的更改,從而實現節(jié)能。物理工具所用的方法,例如單元尺寸調整、管腳交換和 Vth 選擇,只能將稍稍降低功耗而已。

UPF 主要用于增強漏泄功耗的功率門控,其主要用途是定義電壓域。指定不同電壓域的其中一個原因是為了協(xié)商功耗與性能之間的折衷方案。較高的電壓可獲得更快的速度,但需要更高的動態(tài)功耗 (1/2 C V2 f)。

功耗與電壓的平方成正比。因此,降低動態(tài)功耗要從針對設計中的不同模塊規(guī)劃合適的電壓電平開始。動態(tài)功耗主要受活動影響。設計中運行的工作越多,最終需要的能量就越多。隨著在設計中完成工作的速度提高,所需功耗也會增加。要節(jié)省動態(tài)功耗,可以降低設計的工作速度(降低時鐘速度),嘗試降低電壓,或嘗試削減設計活動。減小設計中的電容是節(jié)能的另一個重要方面,這通??山柚咝У膶嵤┗蛲ㄟ^調整工藝來實現。

一般而言,設計架構師比較擅長確定電壓和時鐘速度。但目前為止,還未找到減少活動(尤其是不必要的活動)的有效做法。此類縮減往往需要微架構更改(例如 FSM 重新編碼、模塊級時鐘門控、存儲器門控、存儲器分塊和旁路存儲器訪問),而這類更改要求深入了解設計功能。這類更改適合由編寫 RTL 的設計人員來執(zhí)行。

在許多公司,降低功耗的工作交給功耗專家完成。這些專家具備多年積累的反復應用于所在業(yè)務組設計的知識和方法。但這種方法非常狹隘,無法在公司內多個業(yè)務組之間拓展。

公司開始認識到這一方法的局限性。于是越來越多的 RTL 設計人員從一開始便承擔了解決功耗問題的任務。理想情況下原本就應如此。了解設計的人員是進行功耗優(yōu)化的最佳人選。而且,在設計轉向 FinFET 技術的過程中,動態(tài)功耗已成為功耗的主導因素(圖 1)。

圖 1:功耗趨勢。

降低 RTL 動態(tài)功耗的常用方法

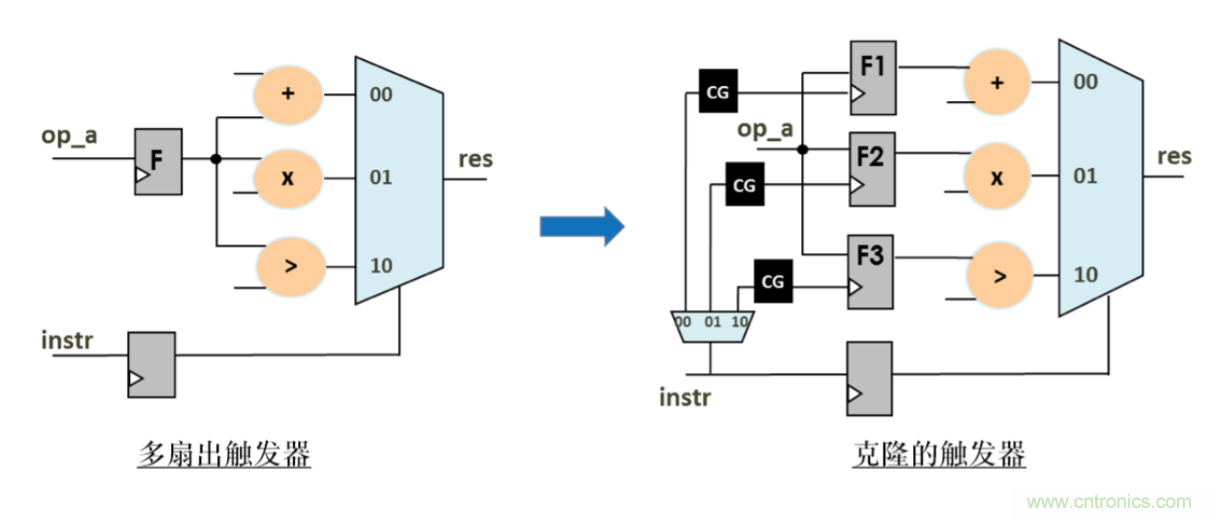

在 RTL 做出的決定對設計功耗的影響遠大于在設計流程后期做出的決定。RTL 設計人員嚴重依賴時鐘門控來削減時鐘翻轉。這是目前占絕對優(yōu)勢的降低動態(tài)功耗的最常用方法。RTL 設計人員使用的一些其他方法包括數據門控和觸發(fā)器克?。蚕恚▓D 2)。

圖 2:克隆觸發(fā)器方法。

圖 2 顯示:

• 觸發(fā)器 F 提供了用于 3 種算術運算的運算符。

• 觸發(fā)器 F 無法進行門控,因為至少一種算術運算需要它的值。

• 即便執(zhí)行一種運算,另外兩種運算中的邏輯也會發(fā)生不必要的翻轉并產生功耗。

• 通過將觸發(fā)器 F 克隆到三個觸發(fā)器(F1、F2 和 F3)中,可在對兩種運算進行門控的同時計算第三種運算。

通過這一更改,設計人員需要確認額外觸發(fā)器的功耗要遠小于它們所控制的下游算術運算功耗。

要對功耗產生更深刻的影響,RTL 設計人員需要在設計中進行越來越多的粗粒度(微架構)更改。例如,通過以下方法可顯著削減動態(tài)功耗:

• 模塊級的時鐘門控

• 將寄存器鏈轉換為環(huán)形緩沖器

• 關斷存儲器

• 旁路存儲器訪問

• 執(zhí)行重定時

• 使用運算符屏蔽。

將移位寄存器替換為環(huán)形緩沖器是一種常見的微架構設計更改。移位寄存器中的活動量很大,因為沿著接收新值的觸發(fā)器鏈,數據一直都在進行移位。這一移位操作導致觸發(fā)器(以及這些觸發(fā)器所驅動的邏輯中)發(fā)生多次不必要的翻轉并造成功耗。因此,設計人員考慮將移位寄存器替換為環(huán)形緩沖器(圖 3),因為這些緩沖器在讀取或使用新值時不需要移動。

圖 3:將移位寄存器替換為環(huán)形緩沖器。

進行這一更改后,設計人員需要確認在環(huán)形緩沖器內添加讀/寫指針邏輯產生的功耗不會超過通過使用環(huán)形緩沖器節(jié)省的功耗。

由于在任意給定的時間間隔,僅僅訪問總計地址中的少數幾個地址,因此存儲器會浪費功率。為解決此問題,設計人員可使用較小的“分塊”實施總體存儲器,這些分塊在未被訪問時可予以關斷(圖 4)。

圖 4:存儲器分塊示例。

圖 4 顯示了對一個 1024 字存儲器進行分塊的兩種方法:

1. 兩個 512 字的分塊:僅其中一個分塊處于主動被訪問狀態(tài),另一個分塊則通過門控關斷以節(jié)省功耗。

2. 四個 256 字的分塊:任意時刻有三個分塊可處于門控關斷狀態(tài)。

另一種設計存儲器以節(jié)省功耗的方法是通過一組固定寬度的存儲塊來配置所需的存儲器字大小。在圖 5 所示的示例中,有多種實現 512 字 X 28 位存儲器的方法,圖中提供了兩種:

1. 剛好使用 28 位字大小 (16 + 8 + 4) 并插入額外的編碼邏輯,用于在兩個分塊之間做出選擇(圖 5 右上角)。

2. 使用單個 32 位存儲器元器件(圖 5 右下角)。盡管此解決方案不需要任何編碼邏輯,但有 4 位存儲器被浪費。

圖 5:可能的存儲器配置。

不論設計人員采用哪種方法來降低存儲器功耗,都必須非常小心,確保額外解碼邏輯的功耗仍小于較大的原始存儲塊功耗。

遺憾的是,前述方法的接受度遠不如預期。主要有兩個原因:

• 不容易了解設計中存在這類機會。

• 不容易了解通過做出更改將會降低多少功耗。

通常,設計人員依賴他們的經驗或直覺做出設計更改。他們載入仿真波形,并嘗試估計其設計中可能出現冗余活動的位置。然后,根據此類活動所在的區(qū)域,嘗試評估可減少浪費活動的方法。對一般 RTL 設計人員而言,這樣未免要求過高。因此,很多功耗節(jié)省未能付諸實施。使用 PowerPro® 提供了一種解決方案。

使用 POWERPRO 降低動態(tài)功耗

很顯然,傳統(tǒng)的降低功耗方法已經不再行得通。遷移到 FinFET 給動態(tài)功耗帶來了與日俱增的嚴峻挑戰(zhàn)。為保持競爭優(yōu)勢,單純依賴功耗專家來降低功耗已經遠遠不夠了。公司將會在功耗方面落后于競爭對手。

簡單地報告設計的功耗數字已不再適宜。功耗分析是一個重要的步驟,但它本身并不能節(jié)省任何功耗。最終要取決于設計人員個人的專業(yè)知識,以及他們如何解讀工具報告從而優(yōu)化功耗設計。

RTL 設計人員需要關于設計中哪些位置可以節(jié)省功耗的指導。他們需要關于其設計中存在的優(yōu)化范圍(例如模塊級時鐘門控、移位寄存器到環(huán)形緩沖器、存儲器緩存和復位移除)及相關功耗節(jié)省的確鑿證據。PowerPro 在設計中提供了進行許多微架構和細粒度優(yōu)化的可能性,并且呈現了與每項更改相關的實際功耗節(jié)省。與手動方法相比,其可最大限度減少了花費在做出設計決策上的時間?;?PowerPro 的建議,設計人員可根據其設計進度做出更改。如果依據進度還有足夠的時間,他們可以實施所有建議。如果時間有限,設計人員可以選取最佳建議加以實施。在設計流程中采用 PowerPro 時,這一靈活性至關重要。

功耗優(yōu)化的另一個關鍵部分是探索各種更改(例如工作模式、時鐘頻率、工作電壓和工藝技術)對應的功耗的能力,對于 IP 開發(fā)人員而言尤其如此。建議的優(yōu)化應適用于上述所有參數。利用 PowerPro,設計人員可以探索仿真配置文件、電壓、時鐘速度和設計自身的更改。在 PowerPro 內可以并行評估以上多種更改(圖 6)。因此,過去需要幾周才能完成的探索任務,現在只要幾個小時就能完成。這種生產率提升讓 PowerPro 成為極具吸引力的設計流程補充。

圖 6:PowerPro 功耗探索。

檢測功率冗余的基礎技術是形式化分析。PowerPro 對設計執(zhí)行深入的時序分析,以找出存儲器訪問、寄存器載入和數據路徑計算中存在的冗余。由于 PowerPro 能夠基于時序探索建議修改,因此遠優(yōu)于市場中的同類競爭技術。PowerPro 可針對設計流程的所有方面提供支持,包括寫出優(yōu)化的 RTL、ECO 和驗證。設計人員確信,他們可以接受源自 PowerPro 的所有建議,并且不會對其交付進度產生任何不利影響。

推薦閱讀: