【導讀】現今,電子系統(tǒng)往往具有許多不同的電源軌。在采用模擬電路和微處理器、DSP、ASIC、FPGA的系統(tǒng)中,尤其如此。為實現可靠、可重復的操作,必須監(jiān)控各電源電壓的開關時序、上升和下降速率、加電順序以及幅度。既定的電源系統(tǒng)設計可能包括電源時序控制、電源跟蹤、電源電壓/電流監(jiān)控和控制。有各種各樣的電源管理IC可以執(zhí)行時序控制、跟蹤、上電和關斷監(jiān)控等功能。

時序控制和跟蹤器件可以監(jiān)控和控制多個電源軌,其功能可能包括設置開啟時間和電壓上升速率、欠壓和過壓故障檢測、余量微調(在標稱電壓值的一定范圍內調整電源電壓)以及有序關斷。適合這些應用的IC種類眾多,簡單的如利用電阻、電容和比較器構成的純模擬器件,復雜的如高集成度狀態(tài)機和通過 I2C bus.總線進行數字控制的可編程器件。某些情況下,系統(tǒng)的電壓調節(jié)器和控制器可能包括關鍵控制功能.

對于采用多個開關控制器和調節(jié)器的系統(tǒng),還有一個考慮是器件以不同開關頻率工作時,如何將產生的系統(tǒng)噪聲降至最低。常常需要同步調節(jié)器的時鐘,事實上,如今的許多高性能開關控制器和調節(jié)器都可以與外部時鐘同步。

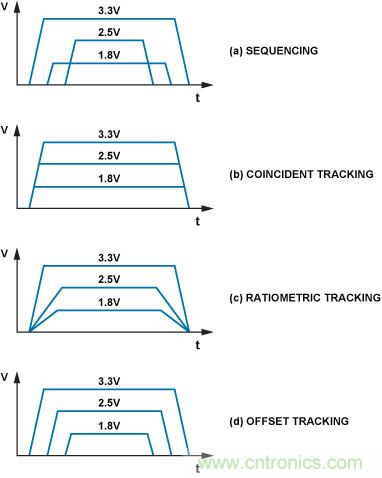

圖1. 電源軌的控制類型

電源時序控制和跟蹤

所謂電源時序控制,是指以指定順序開關電源。電源時序控制可以簡單地基于既定的時間順序,或者一個電源的開啟時間取決于另一個電源何時達到設定的閾值。電源跟蹤基于這樣一個事實:電源電壓無法(一般也不應)瞬間改變。電源系統(tǒng)設計師可以利用這一特性,有效地控制系統(tǒng)中各電源相對于其它電源的斜率。電源跟蹤分為三類:同步、比率和偏移。圖1中的四幅圖對時序控制、同步跟蹤、比率跟蹤和偏移跟蹤進行了比較。

圖1a中,三個電源按一定的時間順序開啟和關閉。首先是3.3 V電源開啟,后續(xù)電源的開啟和關閉延遲時間取決于應用的需要。如果額定最大值要求電源按一定的順序激活,這種簡單的時序控制技術將能確保有源器件的電壓不會超過額定最大值。舉例來說,在ADC驅動的放大器上電之前,我們必須保證ADC的電源存在,否則可能損壞ADC的前端。

圖1b顯示同步跟蹤情況,所有三個電源同時開啟,并且以相同的速率彼此跟蹤,因此最低電源電壓首先建立,然后是較高的電源電壓。電源關斷以相反的方式進行。這個例子很好地說明了舊式FPGA或微處理器應用中電源是如何接通的:首先激活較低的內核電壓,然后接通輔助或I/O電源。稍后將以Xilinx Virtex-5 FPGA的同步跟蹤舉例說明。

圖1c中,電源以不同的斜率上電。如前所述,能夠對電源的斜率dV/dt進行控制是一個非常有用的特性,它可以防止電路中去耦電容的大浪涌電流(充電電流)損壞器件。如果不加限制的話,浪涌電流可能大大超過標稱工作電流。斜率限制可以防止有源器件閂鎖、電容短路、PCB走線受損以及線路保險絲熔斷。

圖1d中,所有電源具有相同的斜率,但其施加時間由預定的失調電壓決定。此類跟蹤適用于需要限制電源電壓差(常常出現在DAC和ADC等混合信號器件的額定最大值部分)的器件,這種方法可以防止器件永久性受損。

基于FPGA的設計示例

使用FPGA系統(tǒng)的供電是探討多電源系統(tǒng)處理的活教材。適當的FPGA電源控制對于實現可靠、可重復的設計至關重要,否則可能會在實驗室甚至現場引發(fā)災難性故障。大多數FPGA具有多個電源軌,一般表示為 VCCO, VCCAUX,和 VCCINT.這些電源分別用于為FPGA內核、輔助電路(如時鐘和PLL等)、接口邏輯供電.

這些電源軌需要考慮的事項可以分為如下幾類:

● 電源軌的時序控制

● 電源軌電壓的容差要求

● 電源可能有軟啟動或斜率控制需求

下面以Xilinx Virtex-5系列FPGA的電源要求為例來說明,該系列提供許多特性,包括邏輯可編程能力、信號處理和時鐘管理。根據數據手冊,Virtex-5的電源上電順序要求為 VCCINT, VCCAUX,和 VCCO.這些電源相對于地的斜坡時間為200 μs(最小值)至50 ms(最大值)。建議工作條件如表1所示。

表1. Xilinx Virtex-5電源軌要求

如前所述,Virtex-5要求同步電壓跟蹤。此外,電源必須在特定的建議工作容差范圍內,而且必須在特定的dV/dt范圍內上升和下降.dV/dt.

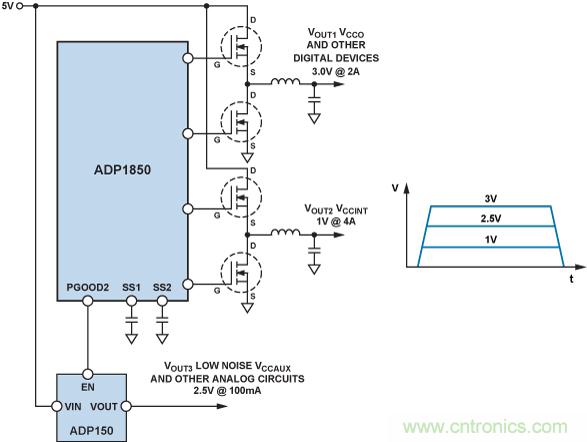

但是,FPGA只是一個較大系統(tǒng)的一部分。為了進一步闡明本例,假設有一個高電流、5 V主系統(tǒng)電源軌。為FPGA內核供電的1 V電源具有±5% (±50 mV)的容差,需要提供最高4 A的電流。3 V電源為通用邏輯電源,具有±5%的容差,在本例中需要提供4 A電流以便為FPGA I/O和設計中的其它邏輯器件供電。2.5 V電源為模擬電源,需要提供低噪聲的100 mA電流.

針對此應用,利用雙通道降壓控制器ADP1850 提供1 V和3 V高電流電源是一個很好的解決方案。ADP1850具有許多特性,其中包括:軟啟動控制、同步跟蹤以及主從電源時序控制。上電時的上升速率由SS1和SS2引腳上的電容控制。本例中,3 V數字電源是主電源。針對2.5 V模擬電源,超低噪聲 低壓差調節(jié)器(LDO)ADP150 是絕佳選擇,它可以利用ADP1850的PGOOD2信號進行時序控制。圖2為該系統(tǒng)的簡化框圖,顯示了時序控制的一般流程,詳情參見ADP1850數據手冊。

圖2. Virtex-5的電源系統(tǒng)

上例說明了時序控制和跟蹤的常見使用方式,可以將其擴展到當今的許多多電源系統(tǒng),包括基于微處理器的系統(tǒng)和涉及混合信號技術(ADC和DAC)的系統(tǒng)。

模擬電壓和電流監(jiān)控(ADM1191)

針對要求精密監(jiān)控多個系統(tǒng)電源電流和電壓的高可靠性應用,可以使用簡單易行的模擬監(jiān)控電路。例如, 數字電源監(jiān)控器 ADM1191 提供1%的測量精度,包括一個用于電流和電壓回讀的12位ADC、一個精密電流檢測放大器以及一路用于提供過流中斷的ALERTB輸出。圖3顯示了ADM1191結合一個主控制器(如微處理器或微控制器等)的應用。

圖3. 簡單的電源電壓和電流監(jiān)控器

ADM1191通過I2C 總線與主控制器通信。通過配置A0和A1引腳的邏輯輸入電平,同一系統(tǒng)最多可以支持16個器件的尋址。本地控制器可以將測得的電壓與電流相乘,從而計算電源軌的功耗。發(fā)生過流狀況時,ALERTB信號通過一個中斷快速通知控制器,這個關于故障狀況的快速報警可以幫助保護系統(tǒng)免遭損壞。

時序控制和監(jiān)控的結合

大型固定系統(tǒng),甚至某些高性能插卡,具有許多需要控制和監(jiān)控的電源軌。圖4涉及到一個具有8個電源軌的復雜電源系統(tǒng)的控制。系統(tǒng)的核心是ADM1066, 它是一款靈活的高集成度超級電源時序控制器Super Sequencer®可提供完整的電源控制功能,特性包括時序控制、監(jiān)控、余量微調和編程能力。ADM106x系列中的其它器件還具有溫度監(jiān)控和看門狗功能。

圖4. 8軌電源系統(tǒng)的控制

8軌系統(tǒng)具有三個主電源軌:12 V、5 V和3 V。其它電源軌則是利用開關調節(jié)器和LDO從這些主電源軌產生。每個調節(jié)器具有一路使能輸入,它由ADM1066的10路可編程驅動器(PD)輸出之一驅動,因此用戶可以按照一定的受控順序使所有電源軌上電。ADM1066具有一個片上電荷泵,可以提升6路PD輸出電壓以提供外部N-MOSFET的高驅動電壓;當需要控制更高電壓的電源時,外部N-MOSFET用作電源軌開關。

ADM1066具有片上EEPROM,用以存儲電源系統(tǒng)控制參數。ADI公司的實用程序 為器件配置提供了便利,大大簡化了上電和運行任務,消除了費時的代碼開發(fā)工作。當系統(tǒng)進一步發(fā)展,以及有新器件加入設計時,可以輕松調整電源序列。時序參數和電壓跳變點很容易重新編程。這個功能非常有用,可以節(jié)省開發(fā)時間,降低電路板開發(fā)可能延誤的風險

數字輸出信號——PWRGD(電源良好)、VALID和SYSRST(系統(tǒng)恢復)——由ADM1066在輪詢時產生,或者通過中斷/數字輸入提供,以便將電源系統(tǒng)的狀態(tài)告知系統(tǒng)微控制器,從而在發(fā)生故障時能夠采取措施。這種快速通知可以防止電容短路和其它危險狀況引發(fā)災難性損害。PWR_ON和/RESET是從系統(tǒng)控制器到ADM1066的數字輸入,用以形成完整的系統(tǒng)控制環(huán)路。

利用ADM1066進行電源余量微調

在系統(tǒng)開發(fā)期間,當設計工程師需要調整電源電壓以優(yōu)化其電平或使其偏離標稱值時,可以使用ADM1066的片內DAC來執(zhí)行電源余量微調。利用這種余量微調特性,可以在電源限制范圍內對系統(tǒng)進行全面特性測試,而不需要使用外部儀器。該功能通常是在在線測試(ICT)期間執(zhí)行,例如:當制造商希望保證受測產品能夠在標稱電源電壓±5%的范圍內正常工作時?;趫D4所示的電路,用戶可以在許多電源軌上實現余量微調。

開環(huán)電源余量微調

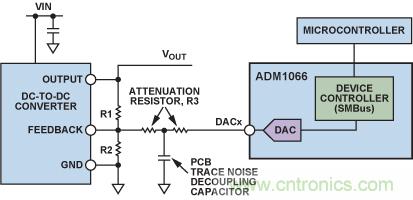

對DC/DC轉換器或LDO等電源進行余量微調的最簡單方法,是將額外電阻切換到電源模塊的反饋節(jié)點中,以改變反饋或調整節(jié)點的電壓,從而利用DAC迫使輸出電壓上調或下調所需的幅度。采用這種衰減器(圖5)時,可以通過SMBus更新相關DAC輸出的值,從而遠程命令ADM11066執(zhí)行電源余量微調。該過程可以利用獨立于系統(tǒng)控制環(huán)路的開環(huán)技術實現。

圖5. 開環(huán)余量微調

ADM1066最多可以為6個電源執(zhí)行開環(huán)余量微調,它利用6個片上電壓輸出DAC(DAC1至DAC6)驅動要微調的電源模塊的反饋引腳。實現這一功能的最簡單電路是利用一個衰減電阻(R3),將DACx引腳連接到DC/DC轉換器的反饋節(jié)點。當DACx輸出電壓設定為與反饋電壓相等時,無電流流入衰減電阻,DC/DC轉換器的輸出電壓不發(fā)生變化。當DACx輸出電壓高于反饋電壓時,電流流入反饋節(jié)點,DC/DC轉換器的輸出必須下降以進行補償。要提升DC/DC轉換器輸出,DACx輸出電壓設定值須低于反饋節(jié)點電壓。為降低噪聲,如圖中所示,可以將該串聯(lián)電阻分成兩個電阻,其間的節(jié)點可以通過一個電容去耦到DC/DC轉換器的地

閉環(huán)電源余量微調

一種更精確、更全面的余量微調方法是在閉環(huán)系統(tǒng)中使用類似的電路。圖4所示為針對1.2 V輸出的一個例子。要微調的電源軌電壓可以通過VX2回讀,確保將其精確調整到目標電壓。ADM1066集成了執(zhí)行微調所需的全部電路,12位逐次逼近型ADC用于讀取受監(jiān)控電壓的電平,6個電壓輸出DAC用于按照上述方法調整電源電平。這些電路可以配合微控制器等其它智能器件使用,以實現閉環(huán)余量微調系統(tǒng),它可以將DC/DC轉換器或LDO電源設定到任何電壓,精度為目標值的±0.5%。

為了在要測試的電源軌上實現閉環(huán)余量微調,請執(zhí)行下列步驟:

1. 禁用6路DACx輸出。

2. DACx輸出電壓設定為反饋節(jié)點電壓

3. 使能DAC

4. 讀取連接到VPx、VH或VXx引腳之一的DC/DC轉換器輸出的電壓。

5. 需要時,提高或降低DACx輸出電壓以調整DC/DC轉換器輸出電壓。否則就停止,目標電壓已經達到。

6. 將DAC輸出電壓設定為某一值,使電源輸出改變所需的幅度(例如±5%)。

7. 重復該過程,直至達到該電源軌所需的電壓

步驟1至3確保各DACx輸出緩沖器開啟時,它對DC/DC轉換器輸出的直接影響非常小。DAC輸出緩沖器的作用是消除上電時的瞬變"毛刺",因為緩沖器首先上電并跟隨引腳電壓,此時它不驅動該引腳。一旦輸出緩沖器正確使能,緩沖器輸入即切換到DAC,緩沖器的輸出級開啟,從而消除輸出毛刺。

開關調節(jié)器的同步

在具有多個電源軌并使用一個以上開關調節(jié)器或控制器的系統(tǒng)中,由于內部開關頻率的差異,這些器件之間可能會相互作用。這會引起拍頻諧波,大幅提高電源噪聲,嚴重影響EMI測試。幸運的是,許多開關控制器和調節(jié)器在設計上都支持內部時鐘同步。LDO不存在這個問題,但其電流輸出有限,并且在大多數情況效率較差,因此有時可能不合需要。

雙通道開關調節(jié)器、ADP2116 就是可同步器件的一個很好的例子。通過SCFG引腳,可將其SYNC/CLKOUT引腳配置為輸入SYNC引腳或輸出CLKOUT引腳。作為輸入SYNC引腳,它可讓ADP2116與外部時鐘同步,兩個通道以外部時鐘頻率的一半、彼此180°錯相工作。

作為輸出CLKOUT引腳,它可提供輸出時鐘,其頻率是通道開關頻率的兩倍且90°錯相。因此,一個配置為CLKOUT的ADP2116可以充當主轉換器,為所有其它DC/DC轉換器(包括其它ADP2116器件)提供外部時鐘(圖6)。配置為從器件時,它接收主器件的外部時鐘并與之同步。通過同步系統(tǒng)內的所有DC/DC轉換器,這種方法可防止產生能導致EMI問題的拍頻諧波。

圖6. 利用外部時鐘同步多個ADP2116

結束語

本文討論多電源系統(tǒng)的處理方法。時序控制器、監(jiān)控器、調節(jié)器和控制器具有非常高的功能集成度,便于設計工程師處理潛在的電源問題,而無需采用全部是分立IC的電路板。這些器件對設計工程師非常有用,可以提高設計成功的概率,降低重新設計的可能性和電路板開發(fā)延誤的風險。

參考電路

Moloney, Alan. “Power Supply Management—Principles, Problems, and Parts.” Analog Dialogue. 40-2. May 2006.

推薦閱讀: